针对?SiC?功率金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)器件进行了抗辐照试验的研究,利用实验室环境模拟空间辐照进行了试验,采用?60Co γ?射线源与测试系统开展了总剂量辐照试验研究,对?SiC MOSFET?器件的阈值电压与导通电阻的漂移进行了表征,得到辐照后阈值电压的漂移小于?0.8 V,导通电阻的变化小于?0.02 ?。同时采用?Br、I、Au?三种离子作为单粒子辐射源,研究了?SiC MOSFET?器件的单粒子栅穿(single event gate rupture,SEGR)和单粒子烧毁(single event burnout,SEB)机制。通过试验获得了?SiC MOSFET?器件抗辐照特性参数,为其在航空、航天等领域中的应用提供了技术参考。

空间辐射辐照环境中存在大量的高能电子、质子、γ?射线和重离子等,将会对空间飞行器中的半导体元件造成威胁。功率金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)器件一般作为空间系统的开关器件,其性能的变化将会引起系统的失效,因此对功率MOSFET器件的抗辐照能力提出了更高的要求[1-2]。

对于多数半导体材料,产生一对电子空穴对需要的平均能量为其禁带宽度的?3~5?倍[3],SiC?材料的禁带宽度比传统?Si?材料大的多,因此辐照引入的电子空穴对更少。材料的临界位移能反映了其抗位移辐照能力,SiC?材料临界位移能是?Si?材料的近?2倍,可减少位移缺陷的产生。SiC?材料具有大的禁带宽度和高的临界位移能,理论上具有很好的抗辐照性能,结合?SiC?材料的抗辐照特性和?MOSFET良好的电学性能,SiC MOSFET?器件是一种很有潜力的抗辐照器件。但是,目前对于?SiC?辐照特性的研究主要还停留在材料的抗辐照性能,国内对于SiC MOSFET?器件的辐照特性研究还在仿真模拟阶段[3-4],试验研究还处于空白。

针对空间环境可采用总剂量辐照、单粒子辐照等方法来研究器件的抗辐照性能。研究表明,总剂量辐照将在?MOSFET?栅氧化层界面处产生陷阱电荷和界面态,引起阈值电压漂移、跨导特性退化、漏电流增加、击穿电压降低等效应。单粒子效应一般会造成功率?MOSFET?栅极漏电增大,引起单粒子栅击穿效应(single event gate rupture,SEGR);另外还可能会造成器件寄生晶体管的雪崩倍增效应,产生大电流,导致单粒子烧毁效应(single event ?burnout,SEB)。

本文通过总剂量辐照和单粒子效应试验模拟空间辐照环境,对?SiC MOSFET?器件的抗辐照能力进行研究。通过总剂量辐照,研究了?SiC MOSFET器件在辐照前后阈值电压与导通电阻的变化;在单粒子效应试验中,主要关注了器件的单粒子烧毁效应和单粒子栅穿效应。通过试验分析,得到了?SiC ?MOSFET?器件抗辐照性能的基本指标,说明了其具有抗辐照应用的潜力,同时探讨了?SiC?器件结构与工艺的抗辐照加固技术。

1、总剂量辐照试验及分析

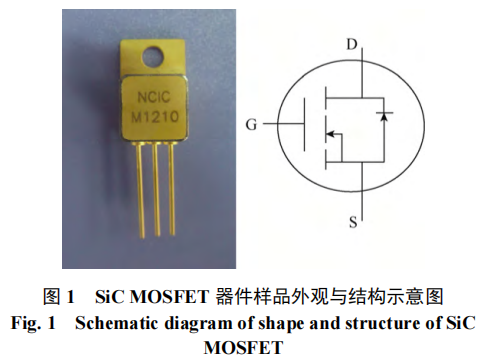

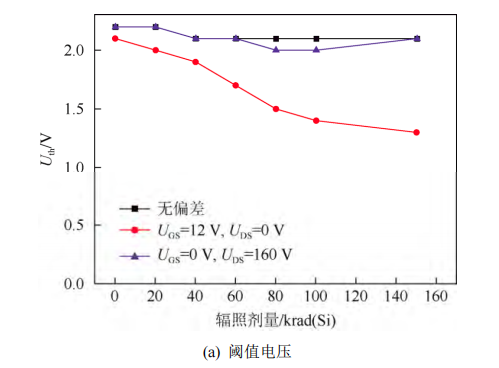

总剂量试验样品采用?SiC MOSFET?器件,TO-257-B?金属陶瓷封装如图?1?所示,测量其器件基本参数,阈值电压?Uth?为?2.2 V,漏源击穿电压UBR?为?1 200 V。总剂量辐照试验在北京师范大学60Co γ?射线源上进行辐照,辐照剂量率为10 rad(Si)/s。为了测试器件的抗辐照性能,试验中?γ?射线直接辐照器件,没有采取屏蔽措施。①在零偏器件测试中,偏置条件为?UGS=0 V,UDS=0 V,在不同的辐照总剂量下测量器件的开启电压?Uth?和开启电阻?Rdson?等电学参数;②对于栅源偏置器件,偏置条件为UGS=12 V,UDS=0 V,在不同总剂量辐照后测量器件参数;③对于漏源偏置器件,偏置条件为?UGS=0 V,UDS=160 V,在不同总剂量辐照后测量器件参数。在阈值电压?Uth?测量时,UDS=UGS,取?ID=1 mA?时为?UGSth;导通电阻测量时,取?UGS=12 V,IDS=7.6 A。

从图?2?试验结果可以看出,在不加栅压的条件下,总剂量辐照引起的阈值电压漂移较小,小于?10%,导通电阻保持在?0.12~0.13 ?,导通电阻变化小于0.01 ?;在施加栅极电压偏置时,总剂量辐照引起的阈值电压漂移明显,辐照总剂量达到?150 krad(Si)时,阈值偏移为?0.8 V,导通电阻在?0.11~0.13 ?。

由于在栅极零偏时,辐照产生的电子空穴大量复合,只有少量空穴被 SiC/SiO2 界面附近的陷阱俘获,因此对 SiC MOSFET 器件的阈值电压和导通电阻影响较小;当栅极加正电压偏置时,辐照产生的电子向栅极漂移,空穴向 SiC/SiO2界面漂移,大量空穴被界面陷阱俘获,形成正氧化层电荷,从而引起器件阈值电压的漂移与导通电阻的变化。

2、单粒子辐照试验及分析

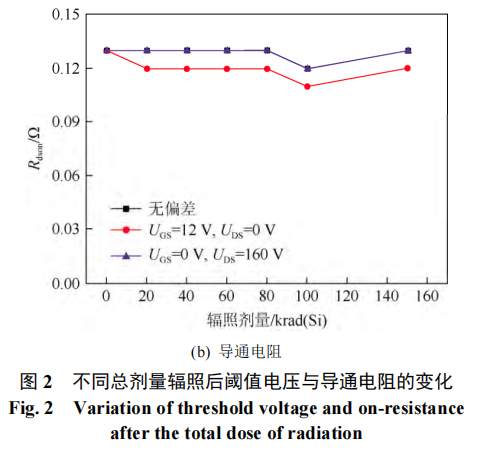

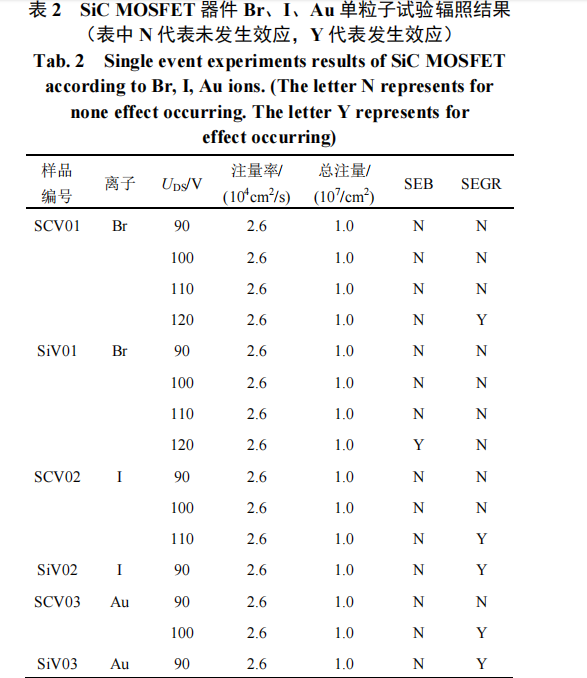

单粒子试验分别采用?Br、I、Au?三种离子作为单粒子辐射源,对?SCV01~SCV03、SiV01~SiV03六个样品进行单粒子辐照试验。单粒子辐照系统如图?3?所示。

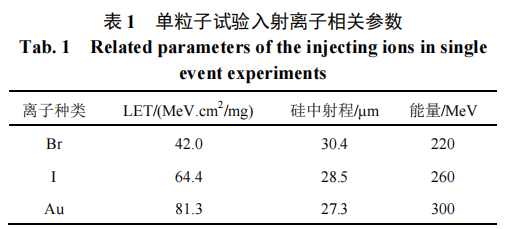

SCV01~SCV03?样品为?SiC MOSFET?器件,采用?TO-257-B?金属陶瓷封装,进行开帽辐照测试;SiV01~SiV03?为国内某型抗辐照?Si VDMOS?器件(漏源击穿电压?200 V)。辐照离子的参数如表?1?所示,其中离子的射程采用的是离子在硅中射程进行标定的。待测器件放置在真空辐照室中,通过远程控制系统对离子的总注量进行监测和控制,同时根据测试要求,通过测试计算机系统选择测试接头,测量?IDSS和?IGSS。测试主要步骤如下:

1)在辐照前,栅极加工作电压?UGS=20 V,测量器件正常工作状态的电流。

2)栅极电压?UGS=0 V,漏极加正电压,从UDS=90 V?开始偏置,进行单粒子辐照试验,当总注量计数达到?1.0×107?/cm2?时停止辐照,测量器件的IGS与?IDS,判断是否发生?SEB?或?SEGR。

3)若未发生?SEB?与?SEGR,则增加漏源电压UDS,重复以上步骤,测试栅源电流与漏源电流;如果发生?SEB?与?SEGR,则可以给出阈值。

如表?2?所示,所有样品栅极电压均为?0 V。对SCV01、SiV01?两个样品,采用?Br?源进行单粒子辐照,参数如表?1?所示,总注量为?1.0×107?/cm2,其中SCV01?在?UDS=120 V?下发生?SEGR,由于样品栅极已经发生破坏性损伤,无法进一步测试?SEB?阈值,但可以看出在测试范围内样品未发生?SEB;SiV01在UDS=120 V下发生SEB。进一步对SCV02与SiV02样品采用?I?源进行单粒子辐照,参数如表?1?所示,总注量为?1.0×107?/cm2,SCV02?样品在?UDS=110 V?下发生?SEGR;SiV02?在?UDS=90 V?下发生?SEGR。对SCV03?与?SiV03?样品,采用?Au?源进行单粒子辐照,参数如表?1?所示,总注量为?1.0×107?/cm2,SCV03样品在?UDS=100 V?下发生?SEGR;SiV03?在?UDS=90 V下发生?SEGR。

可以看出,3?个?SiC MOSFET?样品在测试中首先发生?SEGR,并且随着注入离子?LET?值的增大,击穿阈值不断减小。这主要是由于?SiC MOSFET器件的栅极接地,漏极接正电压,通过单粒子辐照,将在?SiC?漂移区产生电子空穴对,在漏极电场的作用下,电子向漏极移动,空穴在栅极?SiO2/SiC?界面处形成积累,导致栅介质中电场增大,引起栅介质烧毁,造成栅极漏电增大。通过与加固后?Si ?VDMOS?器件比较,可以看出?SiC MOSFET?具有抗单粒子效应潜力。但是?SiC MOSFET?器件由于栅氧层较薄,因此对?SEGR?更为敏感,可以通过对SiC MOSFET?器件的栅氧化层结构改进,适当增加栅氧化层厚度或采用高?K?栅介质等,来提高?SiC ?MOSFET?器件的?SEGR?阈值,进一步提高其抗单粒子效应能力。

3、结论

本文对?SiC MOSFET?器件的抗辐照性能进行了研究,进行了总剂量辐照与单粒子效应试验,为SiC MOSFET?器件在空间电力系统中的应用提供了技术参考。在总剂量辐照试验中,对?SiC MOSFET器件的阈值电压与导通电阻的漂移进行了表征,得到辐照后阈值电压的漂移小于?0.8 V,导通电阻的变化小于?0.02 ?。单粒子效应试验中,通过采用?Br、I、Au?三种重离子对?SiC MOSFET?进行单粒子辐照测试,得到了器件的?SEGR?阈值。通过辐照试验可以看出,SiC MOSFET?器件具有一定的抗辐照能力,但若今后应用于空间元器件中,仍需要对器件栅极进行改进,对栅氧化层进行抗辐照加固,进一步提高?SiC MOSFET?抗辐照性能。(智 能 电 网 ?文献2016?年?11?月)

图片来源:碳化硅MOS与SiC模块技术漫谈

碳化硅MOSFETs与SiC模块产品概览

芯耀

芯耀

447

447